## **AVS 69 abstract - Illustrations**

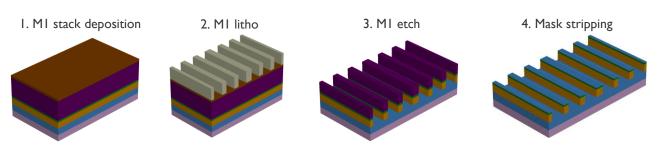

Figure I: Level-I metal (MI) BEOL integration scheme.

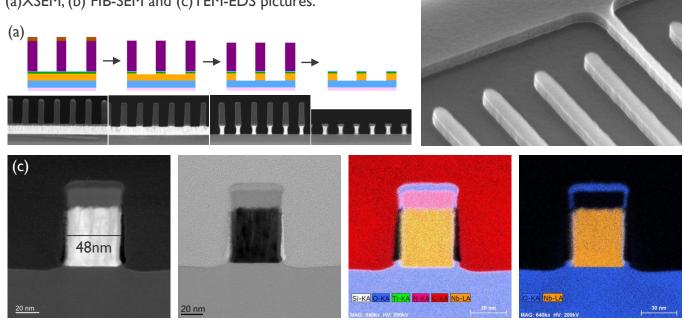

**Figure 2**: Examples of inspections for M1 etch development : (a)XSEM, (b) FIB-SEM and (c)TEM-EDS pictures.

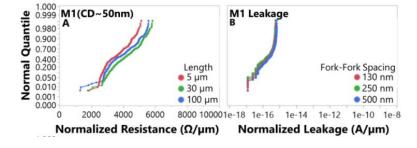

**Figure 3**: (a) Normalized room temp resistance of MI  $Nb_xTi_{(1-x)}N$  lines with 50nm CD. (b) Leakage measurement of MI Fork-Fork structures with 130, 250 and 500nm Fork-Fork spacing.

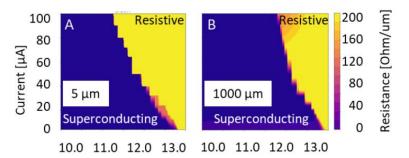

**Figure 4** : Shmoo plots showing Tc and critical current for  $Nb_xTi_{(1-x)}N$  lines with 50nm CD and (a) 5 and (b) 1000  $\mu m$  in length.