## High-Stability and High-Performance PEALD-IZO/IGZO Top-Gate Thin-Film Transistor via Nano-Scale Thickness Control

Yoon-Seo Kim<sup>a</sup>, Won-Bum Lee<sup>a</sup>, Hye-Jin Oh<sup>a</sup>, TaeHyun Hong<sup>a</sup>, and Jin-Seong Park<sup>a,\*</sup>

<sup>a</sup>Division of Materials Science and Engineering, Hanyang University, 222 Wangsimni-ro, Seongdong-gu, Seoul 04763, Republic of Korea

## Supplemental Document

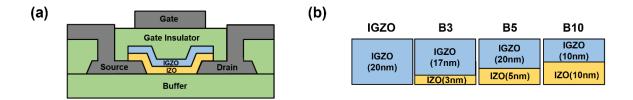

Figure 1a,b illustrates the schematics of the bilayer IZO/IGZO top gate TFTs and active layer thickness split which increased the IZO thickness from 0 nm to 10 nm while the total thickness was fixed at 20nm.

Figure 1. The schematics of (a) the bilayer IZO/IGZO top gate TFT structure and (b) PEALD-IZO/IGZO active layer thickness split.

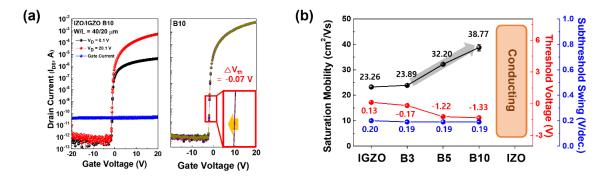

Figure 2a shows that representative transfer curve and positive bias temperature stress (PBTS) of an IZO/IGZO TFT (B10) with a mobility( $\mu$ FE) of 38.77 cm2/Vs and  $\Delta V_{th}$  of -1.33 V, respectively. Figure 2b is the electrical characteristic of the IZO/IGZO TFTs that shows the increase of mobility proportionally according to the IZO thickness, showing the highest mobility in B10 device.

Figure 2. (a) The transfer curve and PBTS of an IZO/IGZO TFT (B10) and (b) the electrical characteristic of the IZO/IGZO TFTs according to the IZO thickness